# Jetson TK1 Development Kit Specification

#### Abstract

This document contains recommendations and guidelines for engineers to follow to create modules for the expansion connectors on the Jetson TK1 Development Kit as well as understand the capabilities of the other dedicated interface connectors and associated power solutions.

November 2014

DA-07507-001 Version 01

#### Notice

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS, AND OTHER DOCUMENTS (TOGETHER AND SEPARATELY, "MATERIALS") ARE BEING PROVIDED "AS IS." NVIDIA MAKES NO WARRANTIES, EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE WITH RESPECT TO THE MATERIALS, AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OR CONDITION OF TITLE, MERCHANTABILITY, SATISFACTORY QUALITY, FITNESS FOR A PARTICULAR PURPOSE AND ON-INFRINGEMENT, ARE HEREBY EXCLUDED TO THE MAXIMUM EXTENT PERMITTED BY LAW.

Information furnished is believed to be accurate and reliable. However, NVIDIA Corporation assumes no responsibility for the consequences of use of such information or for any infringement of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of NVIDIA Corporation. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. NVIDIA Corporation products are not authorized for use as critical components in life support devices or systems without express written approval of NVIDIA Corporation.

#### Trademarks

NVIDIA, the NVIDIA logo and Tegra are trademarks or registered trademarks of NVIDIA Corporation in the United States and other countries. Other company and product names may be trademarks of the respective companies with which they are associated.

#### Copyright

© 2014 NVIDIA Corporation. All rights reserved.

### Table of Contents

| 1.0 Introduction                                                                                                                                                                                                                                                                                                                                         | 3                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 1.1 Abbreviations and Definitions                                                                                                                                                                                                                                                                                                                        | 3                                                                                            |

| 1.2 Jetson TK1 – High Level Definition Summary                                                                                                                                                                                                                                                                                                           | 4                                                                                            |

| 1.3 Feature List                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

| 1.4 Jetson Block Diagram                                                                                                                                                                                                                                                                                                                                 | 5                                                                                            |

| 2.0 Jetson Custom Expansion Interface Connections                                                                                                                                                                                                                                                                                                        | 7                                                                                            |

| 2.1 Display/Touch Expansion Header                                                                                                                                                                                                                                                                                                                       | 7                                                                                            |

| 2.1.1 Display Guidelines                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

| 2.1.2 Touch Guidelines                                                                                                                                                                                                                                                                                                                                   |                                                                                              |

| 2.1.3 I2C Design Guidelines                                                                                                                                                                                                                                                                                                                              |                                                                                              |

| 2.2 General Expansion Header                                                                                                                                                                                                                                                                                                                             | 15                                                                                           |

| 2.2.1 Camera/CSI Guidelines                                                                                                                                                                                                                                                                                                                              |                                                                                              |

| 2.2.2 HSIC Guidelines                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| 2.2.3 I2C Guidelines                                                                                                                                                                                                                                                                                                                                     |                                                                                              |

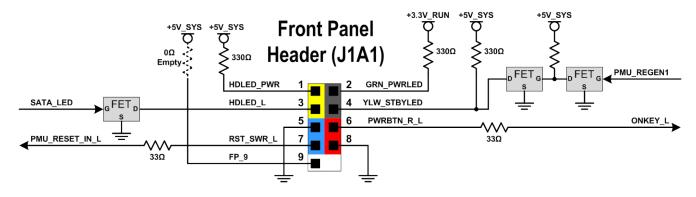

| 2.3 Front Panel Header Slot                                                                                                                                                                                                                                                                                                                              |                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

| 3.0 Jetson Standard Expansion Connectors                                                                                                                                                                                                                                                                                                                 |                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                          | 24                                                                                           |

| 3.0 Jetson Standard Expansion Connectors                                                                                                                                                                                                                                                                                                                 | 24                                                                                           |

| 3.0 Jetson Standard Expansion Connectors<br>3.1 Mini-PCle Expansion Slot                                                                                                                                                                                                                                                                                 |                                                                                              |

| 3.0 Jetson Standard Expansion Connectors<br>3.1 Mini-PCle Expansion Slot<br>3.1.1 PCle Design Guidelines                                                                                                                                                                                                                                                 |                                                                                              |

| 3.0 Jetson Standard Expansion Connectors<br>3.1 Mini-PCle Expansion Slot                                                                                                                                                                                                                                                                                 | 24<br>24<br>27<br>28<br>29                                                                   |

| <ul> <li>3.0 Jetson Standard Expansion Connectors</li> <li>3.1 Mini-PCle Expansion Slot</li> <li>3.1.1 PCle Design Guidelines</li> <li>3.1.2 USB 2.0 Design Guidelines</li> <li>3.1.3 I2C Design Guidelines</li> </ul>                                                                                                                                   | 24<br>24<br>27<br>28<br>29<br>29                                                             |

| <ul> <li>3.0 Jetson Standard Expansion Connectors</li> <li>3.1 Mini-PCle Expansion Slot</li> <li>3.1.1 PCle Design Guidelines</li> <li>3.1.2 USB 2.0 Design Guidelines</li> <li>3.1.3 I2C Design Guidelines.</li> <li>3.2 USB Ports</li> </ul>                                                                                                           | 24<br>24<br>27<br>28<br>29<br>29<br>29<br>30                                                 |

| <ul> <li>3.0 Jetson Standard Expansion Connectors</li> <li>3.1 Mini-PCle Expansion Slot</li> <li>3.1.1 PCle Design Guidelines</li> <li>3.1.2 USB 2.0 Design Guidelines</li> <li>3.1.3 I2C Design Guidelines</li> <li>3.2 USB Ports</li> <li>3.3 Gigabit LAN</li> </ul>                                                                                   | 24<br>24<br>27<br>28<br>29<br>29<br>29<br>30<br>30                                           |

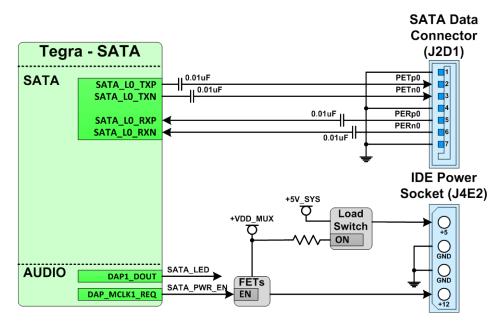

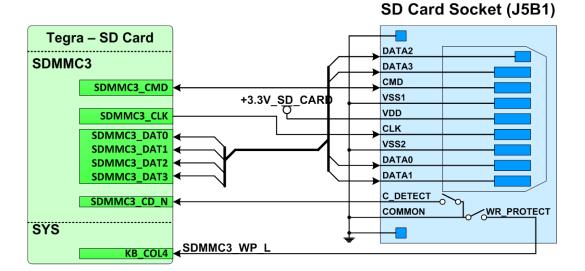

| <ul> <li>3.0 Jetson Standard Expansion Connectors</li> <li>3.1 Mini-PCle Expansion Slot</li> <li>3.1.1 PCle Design Guidelines</li> <li>3.1.2 USB 2.0 Design Guidelines</li> <li>3.1.3 I2C Design Guidelines</li> <li>3.2 USB Ports</li> <li>3.3 Gigabit LAN</li> <li>3.4 SATA</li> <li>3.5 SD Card</li> <li>3.6 HDMI</li> </ul>                          | 24<br>24<br>27<br>28<br>29<br>29<br>29<br>30<br>30<br>31<br>31                               |

| <ul> <li>3.0 Jetson Standard Expansion Connectors</li> <li>3.1 Mini-PCle Expansion Slot</li> <li>3.1.1 PCle Design Guidelines</li> <li>3.1.2 USB 2.0 Design Guidelines</li> <li>3.1.3 I2C Design Guidelines</li> <li>3.2 USB Ports</li> <li>3.3 Gigabit LAN</li> <li>3.4 SATA</li> <li>3.5 SD Card</li> </ul>                                            | 24<br>24<br>27<br>28<br>29<br>29<br>29<br>30<br>30<br>31<br>31                               |

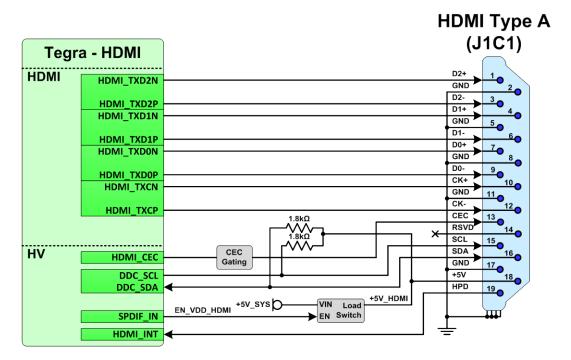

| <ul> <li>3.0 Jetson Standard Expansion Connectors</li> <li>3.1 Mini-PCle Expansion Slot</li> <li>3.1.1 PCle Design Guidelines</li> <li>3.1.2 USB 2.0 Design Guidelines</li> <li>3.1.3 I2C Design Guidelines</li> <li>3.2 USB Ports</li> <li>3.3 Gigabit LAN</li> <li>3.4 SATA</li> <li>3.5 SD Card</li> <li>3.6 HDMI</li> </ul>                          | 24<br>24<br>27<br>28<br>29<br>29<br>29<br>30<br>30<br>30<br>31<br>31<br>31<br>32             |

| <ul> <li>3.0 Jetson Standard Expansion Connectors</li> <li>3.1 Mini-PCle Expansion Slot</li> <li>3.1.1 PCle Design Guidelines</li> <li>3.1.2 USB 2.0 Design Guidelines</li> <li>3.1.3 I2C Design Guidelines</li> <li>3.2 USB Ports</li> <li>3.3 Gigabit LAN</li> <li>3.4 SATA</li> <li>3.5 SD Card</li> <li>3.6 HDMI</li> <li>3.7 Serial Port</li> </ul> | 24<br>24<br>27<br>28<br>29<br>29<br>29<br>30<br>30<br>30<br>31<br>31<br>31<br>31<br>32<br>33 |

# 1.0 Introduction

### 1.1 Abbreviations and Definitions

The following table lists abbreviations that may be used throughout this document and their definitions.

| Abbreviation | Definition                                          |

|--------------|-----------------------------------------------------|

| BT           | Bluetooth                                           |

| CEC          | Consumer Electronic Control                         |

| DDR3L        | Double Data Rate DRAM, Third-generation             |

| eMMC         | Embedded MMC                                        |

| GPS          | Global Positioning System                           |

| HDMI         | High Definition Multimedia Interface                |

| HSIC         | High Speed Inter Chip Interface                     |

| 12C          | Inter IC                                            |

| 125          | Inter IC Sound Interface                            |

| LCD          | Liquid Crystal Display                              |

| LDO          | Low Dropout (voltage regulator)                     |

| LVDS         | Low Voltage Differential Signaling Interface        |

| PCIe         | Peripheral Component Interconnect Express interface |

| PCM          | Pulse Code Modulation                               |

| РНҮ          | Physical Interface (i.e. USB PHY)                   |

| PMC          | Power Management Controller                         |

| PMU          | Power Management Unit                               |

| RF           | Radio Frequency                                     |

| SATA         | Serial "AT" Attachment interface                    |

| SDIO         | Secure Digital I/O Interface                        |

| SPI          | Serial Peripheral Interface                         |

| UART         | Universal Asynchronous Receiver-Transmitter         |

| USB          | Universal Serial Bus                                |

| WiFi (WLAN)  | Wireless Local Area Network                         |

#### Table 1. Abbreviations and Definitions

### 1.2 Jetson TK1 - High Level Definition Summary

Jetson is a low cost Tegra K1 developer kit intended to enable OEM's to evaluate the Tegra K1 architecture and then create a customized design that matches their exact requirements. Jetson provides basic boot options with expansion connectors to enable unused ports to be interfaced with customized hardware.

### 1.3 Feature List

#### **Applications Processor**

- Tegra K1 processor, CD575M

- 23x23mm ,0.7mm pitch

#### DRAM

- DDR3L-1866, 2GB

- Hynix H5TC4G63AFR-RDA

- 4 x 4Gb x16 memory (64 bit width)

#### Flash (Boot/Storage)

- SPI Flash: Winbond W25Q32DW, 32Mbit

- eMMC: Sandisk SDIN8DE4-16G-Q

- 16GB, 4.51

- Full Size SD Card

- SATA Connector

#### HDMI

HDMI Type A

#### USB

- 1x USB 3.0 Type A

- 1x USB 2.0 Micro AB

#### Audio

- Codec: Realtek ALC5639

- 3.5mm Microphone Jack

- 3.5mm Headset Jack

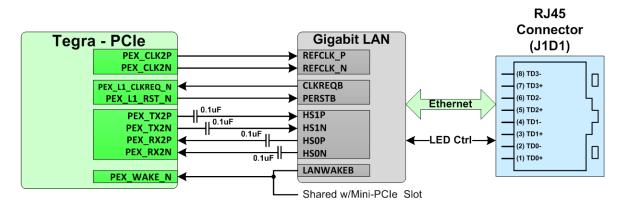

#### LAN

- Realtek RTL8111GS Gigabit MAC/PHY

- PCIe (x1 lane), RJ45 Connector

#### **UI & Indicators**

Power, Reset & Force Recovery Buttons

#### Sensors

Temp Sensor: TMP451

#### Debug

- JTAG: Standard 20-pin header

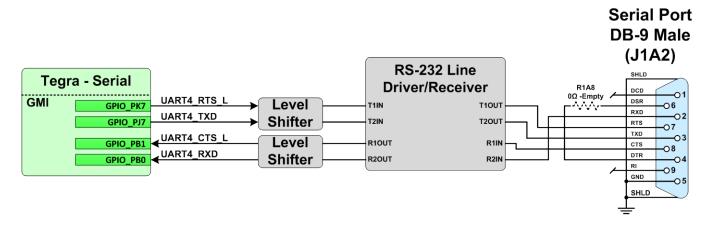

- UART: RS232, D-Sub 9 Connector

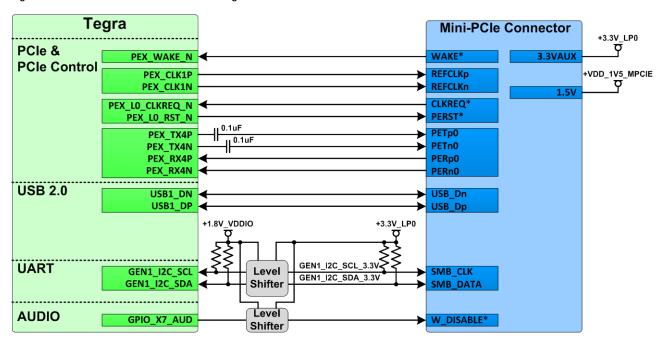

#### Mini-PCIe Connector

- PCIe x1 Lane

- USB 2.0

- I2C (3.3V)

- WLAN Control/LEDs

#### **Display/Touch Expansion Header**

- LVDS/eDP x4 Lanes

- Hot Plug Detect

- Backlight Enable/PWM

- Touch Controller Support

- SPI, I2C

- Clock, Shutdown, Reset

#### **General Expansion Header**

- Camera Support

- CSI: 1 x4 + 1 x1

- CLK, I2C & Control

- Dedicated Power Rails

- HSIC

- UART

- GPIOs

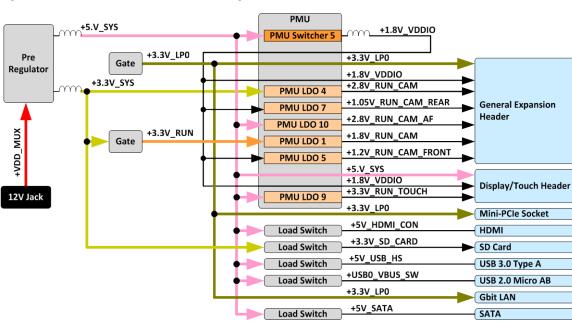

#### Power

- PMU: AMS AS3722, BCTT-09

- CPU Supply: AS3728 Power Stages (x3)

- GPU Supply: AS3728 Power Stages (x2)

- CORE Supply: AS3728 Power Stage

- Pre-Regulators: TI TPS51220

- 12V DC Jack

#### PCB Technology

6-layer, Standard Technology

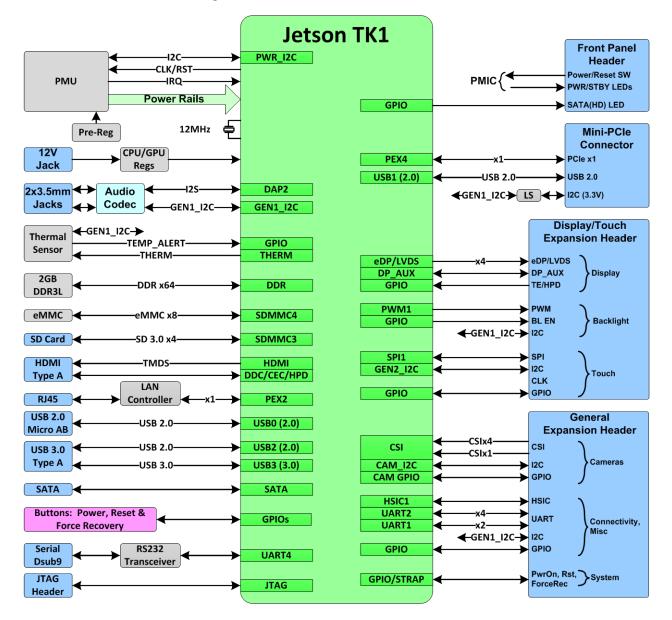

### 1.4 Jetson Block Diagram

17

18

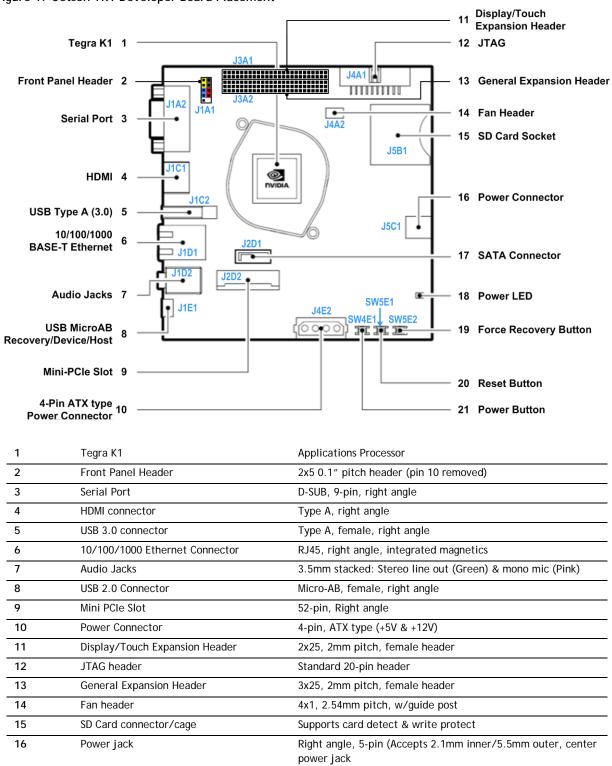

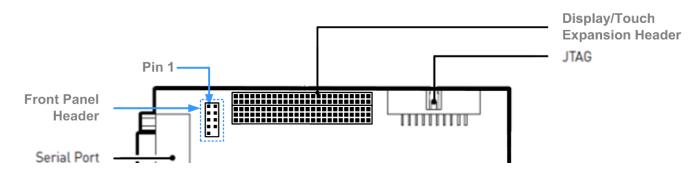

Figure 1. Jetson TK1 Developer Board Placement

Vertical, Standard

Green

SATA connector

Power LED

# 2.0 Jetson Custom Expansion Interface Connections

The Jetson TK1 Developer Kit supports two custom expansion headers:

- Display/Touch Expansion Header, 2mm pitch (2x25 configuration)

- General Expansion Header, 2mm pitch (3x25 configuration)

**Notes:** Display/Touch & General Expansion Headers form 5x25 pin array. The headers can be used together for a single module, or separately for two modules, but if to be used concurrently, ensure the boards do not physically interfere with each other.

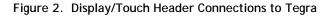

### 2.1 Display/Touch Expansion Header

The Jetson board includes a 2x25, 2mm pitch female expansion header (reference designator J3A1). This includes interface options for an embedded display and touch controller including:

- LVDS / eDP (4-lane) for embedded displays

- LCD Enable & PWM for embedded backlight control

- GEN1 I2C for LVDS display control

- DP\_AUX & HPD for eDP display control & Hot Plug Detect

- SPI & GEN2\_I2C (3.3V) options for Touch control

- Touch controller clock, reset & shutdown

Table 2. Display / Touch Expansion Header Pin Descriptions

| Pin<br># | Signal Name       | Tegra K1 Ball | Usage/Description                                        | Type/Dir<br>Default  | Associated<br>Voltage Rail | Tegra Pad<br>Type |

|----------|-------------------|---------------|----------------------------------------------------------|----------------------|----------------------------|-------------------|

| 1        | +5V_SYS           | NA            | Main 5V from system                                      | Power                |                            |                   |

| 2        | GND               | NA            | Tied to common GND                                       | Ground               |                            |                   |

| 3        | +1.8V_VDDIO       | NA            | Main 1.8V supply from PMU switcher 5                     | Power                |                            |                   |

| 4        | TS_SPI_SCK        | ULPI_NXT      | SPI clock for Touchscreen controller (if SPI used)       | Input                | +1.8V_VDDIO                | ST                |

| 5        | TS_SPI_MOSI       | ULPI_CLK      | SPI MOSI for Touchscreen controller (if SPI used)        | Input                | +1.8V_VDDIO                | ST                |

| 6        | TS_SPI_CS_L       | ULPI_STP      | SPI chip select for Touchscreen controller (if SPI used) | Input                | +1.8V_VDDIO                | ST                |

| 7        | TS_SPI_MISO       | ULPI_DIR      | SPI MISO for Touchscreen controller (if SPI used)        | Output               | +1.8V_VDDIO                | ST                |

| 8        | GND               | NA            | Tied to common GND                                       | Ground               |                            |                   |

| 9        | GND               | NA            | Tied to common GND                                       | Ground               |                            |                   |

| 10       | +3.3V_RUN_TOUCH   | NA            | AMS PMIC LDO9                                            | Power                |                            |                   |

| 11       | TS_SHDN_L         | GPIO_PK1      | Shutdown control for Touchscreen controller              | Input                | +1.8V_VDDIO                | CZ                |

| 12       | TS_CLK            | CLK2_OUT      | Clock for Touchscreen controller                         | Input                | +1.8V_VDDIO                | ST                |

| 13       | TS_RESET_L        | GPIO_PK4      | Reset for Touchscreen controller                         | Input                | +1.8V_VDDIO                | CZ                |

| 14       | GND               | NA            | Tied to common GND                                       | Ground               |                            |                   |

| 15       | GND               | NA            | Tied to common GND                                       | Ground               |                            |                   |

| 16       | +3.3V_SYS         | NA            | Main 3.3V supply                                         | Power                |                            |                   |

| 17       | GPIO_PK2          | GPIO_PK2      | Available GPIO                                           | Output               | +1.8V_VDDIO                | CZ                |

| 18       | GEN2_I2C_SCL_3.3V | GEN2_I2C_SCL  | 3.3V I2C IF (Pulled up to +3.3V_LPO)                     | Input, Open<br>Drain | +3.3V_LP0                  | DD                |

| 19       | +1.8V_VDDIO       | NA            | Main 1.8V supply from PMU switcher 5                     | Power                |                            |                   |

| 20       | GEN2_I2C_SDA_3.3V | GEN2_I2C_SDA  | 3.3V I2C IF (Pulled up to +3.3V_LPO)                     | Bidir, Open<br>Drain | +3.3V_LP0                  | DD                |

| 21       | GEN1_I2C_SCL      | GEN1_I2C_SCL  | 1.8V I2C (Pulled to +1.8V_VDDIO)                         | Input, Open<br>Drain | +1.8V_VDDIO                | DD                |

| 22       | +3.3V_RUN         | NA            | +3.3V rail that is off in LP0                            | Power                |                            |                   |

| 23       | GEN1_I2C_SDA      | GEN1_I2C_SDA  | 1.8V I2C (Pulled to +1.8V_VDDIO)                         | Bidir, Open<br>Drain | +1.8V_VDDIO                | DD                |

| Pin<br># | Signal Name | Tegra K1 Ball | Usage/Description                                   | Type/Dir<br>Default | Associated<br>Voltage Rail | Tegra Pad<br>Type |

|----------|-------------|---------------|-----------------------------------------------------|---------------------|----------------------------|-------------------|

| 24       | EN_AVDD_LCD | NA            | Enable for Embedded display from PMU GPIO4          | Input               |                            |                   |

| 25       | +VDD_MUX    | NA            | Main 12V from Jack                                  | Power               |                            |                   |

| 26       | GND         | NA            | Tied to common GND                                  | Ground              |                            |                   |

| 27       | EN_VDD_BL   | DAP3_DOUT     | Backlight supply enable                             | Input               | +1.8V_VDDIO                | ST                |

| 28       | DP_AUX_P    | DP_AUX_P      | eDP AUX control interface (+)                       | Bidir               | +1.05V_RUN_AVDD            | LVDS/DP           |

| 29       | GND         | NA            | Tied to common GND                                  | Ground              |                            |                   |

| 30       | DP_AUX_N    | DP_AUX_N      | eDP AUX control interface (-)                       | Bidir               | +1.05V_RUN_AVDD            | LVDS/DP           |

| 31       | LVDS_TXD0_P | LVDS_TXD0_P   | LVDS Data lane 0 (+) or eDP Data lane 2 (+)         | Input               | +1.05V_RUN_AVDD            | LVDS/DP           |

| 32       | GND         | NA            | Tied to common GND                                  | Ground              |                            |                   |

| 33       | LVDS_TXDO_N | LVDS_TXDO_N   | LVDS Data lane 0 (-) or eDP Data lane 2 (-)         | Input               | +1.05V_RUN_AVDD            | LVDS/DP           |

| 34       | LVDS_TXD1_P | LVDS_TXD1_P   | LVDS Data lane 1 (+) or eDP Data lane 1 (+)         | Input               | +1.05V_RUN_AVDD            | LVDS/DP           |

| 35       | GND         | NA            | Tied to common GND                                  | Ground              |                            |                   |

| 36       | LVDS_TXD1_N | LVDS_TXD1_N   | LVDS Data lane 1 (-) or eDP Data lane 1 (-)         | Input               | +1.05V_RUN_AVDD            | LVDS/DP           |

| 37       | LVDS_TXD3_P | LVDS_TXD3_P   | LVDS Data lane 3 (+) - Not used for eDP             | Input               | +1.05V_RUN_AVDD            | LVDS/DP           |

| 38       | GND         | NA            | Tied to common GND                                  | Ground              |                            |                   |

| 39       | LVDS_TXD3_N | LVDS_TXD3_N   | LVDS Data lane 3 (-) - Not used for eDP             | Input               | +1.05V_RUN_AVDD            | LVDS/DP           |

| 40       | LVDS_TXD2_P | LVDS_TXD2_P   | LVDS Data lane 2 (+) or eDP Data lane 0 (+)         | Input               | +1.05V_RUN_AVDD            | LVDS/DP           |

| 41       | GND         | NA            | Tied to common GND                                  | Ground              |                            |                   |

| 42       | LVDS_TXD2_N | LVDS_TXD2_N   | LVDS Data lane 2 (-) or eDP Data lane 0 (-)         | Input               | +1.05V_RUN_AVDD            | LVDS/DP           |

| 43       | LVDS_TXD4_N | LVDS_TXD4_N   | LVDS Clock lane (+) or eDP Data lane 3 (+)          | Input               | +1.05V_RUN_AVDD            | LVDS/DP           |

| 44       | GND         | NA            | Tied to common GND                                  | Ground              |                            |                   |

| 45       | LVDS_TXD4_P | LVDS_TXD4_P   | LVDS Clock lane (-) or eDP Data lane 3 (-)          | Input               | +1.05V_RUN_AVDD            | LVDS/DP           |

| 46       | EDP_HPD     | DP_HPD        | eDP display Hot Plug Detect input                   | Output              | +3.3V_LP0                  | ST                |

| 47       | GND         | NA            | Tied to common GND                                  | Ground              |                            |                   |

| 48       | LCD_BL_EN   | GPIO_PH2      | Backlight enable                                    | Input               | +1.8V_VDDIO                | CZ                |

| 49       | LCD_TE      | KB_ROW6       | Tearing Effect from embedded display (if supported) | Output              | +1.8V_VDDIO                | ST                |

| 50       | LCD_BL_PWM  | GPIO_PH1      | Backlight PWM                                       | Input               | +1.8V_VDDIO                | CZ                |

Notes: -

In the Type/Dir column, Output is from Module. Input is to Module. Bidir is for Bidirectional signals.

See Section 5.0 for details on the standard Tegra Pad Types (ST, CZ & DD)

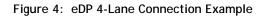

#### 2.1.1 Display Guidelines

Jetson supports up to a 4-lane single-link LVDS interface or up to a 4-lane eDP interface. The maximum resolution supported with LVDS is 1920x1200 @ 60fps (24bpp color depth). With eDP, the maximum supported using the full 4 lanes is 3200x2000 @ 60fps. LVDS and eDP are multiplexed on the same pins. See LVDS/eDP Pin Assignment Options table below for pin assignments for each interface.

| Tegra Ball     | LVDS (3-lane)   | LVDS (4 lane)   | eDP        |

|----------------|-----------------|-----------------|------------|

| LVDS0_TXD0_P/N | LVDS lane 0     | LVDS lane 0     | eDP lane 2 |

| LVDS0_TXD1_P/N | LVDS lane 1     | LVDS lane 1     | eDP lane 1 |

| LVDS0_TXD2_P/N | LVDS lane 2     | LVDS lane 2     | eDP lane 0 |

| LVDS0_TXD3_P/N | N/A             | LVDS lane 3     | N/A        |

| LVDS0_TXD4_P/N | LVDS clock lane | LVDS clock lane | eDP lane 3 |

#### Table 3. eDP/LVDS Pin Assignment Options

### Figure 5: LVDS 4-Lane Connection Example

| Tegra - LVDS                                 |         | Display/                     |          | LVDS Connector          |

|----------------------------------------------|---------|------------------------------|----------|-------------------------|

| LVDS/eDP                                     | <b></b> | Touch<br>Expansion<br>Header | <b>→</b> | YON_N<br>YON_P<br>Y1N_N |

| LVDS0_TXD1_P<br>LVDS0_TXD2_N<br>LVDS0_TXD2_P | →<br>→  |                              |          | Y1N_P<br>Y2N_N<br>Y2N_P |

| LVDS0_TXD3_N<br>LVDS0_TXD3_N<br>LVDS0_TXD4_N |         |                              | <b></b>  | Y3N_N<br>Y3N_P<br>CLK_N |

| LVDS0_TXD4_P<br>SYS KB_ROW6                  | →<br>◆  |                              | →<br>◆>  | CLK_P<br>Tearing Effect |

| UART<br>GEN1_I2C_SCL<br>GEN1_I2C_SDA         |         |                              | <b>→</b> | 12C                     |

#### eDP Design Guidelines

#### Table 4. eDP (RBR / HBR) Main Link Signal Routing Requirements

| Parameter                                       | Requirement | Units             | Notes                                                                                                |

|-------------------------------------------------|-------------|-------------------|------------------------------------------------------------------------------------------------------|

| Max Data Rate (per data lane)                   | 5.4         | Gbps              |                                                                                                      |

| Min UI                                          | 185         | ps                |                                                                                                      |

| Number of Loads                                 | 1           | load              |                                                                                                      |

| Тороlоду                                        |             |                   | Point-Point, Differential, Unidirectional                                                            |

| Termination                                     | 100         | Ω                 | On die at TX/RX                                                                                      |

| Reference plane                                 | GND         |                   |                                                                                                      |

| Max PCB breakout length                         | 7.63        | mm                |                                                                                                      |

| Trace Impedance Diff pair / Single Ended        | 90 / 45-60  | Ω                 | +15%                                                                                                 |

| Max trace length from Tegra TX pin to connector | 215 (1480)  | mm (ps)           | See Note 1. 175ps/inch delay assumed                                                                 |

| Max number of signal vias                       | 4           |                   |                                                                                                      |

| PCB pair-to-pair spacing                        | 3x          | dielectric height | 3x of the thinner of above and below                                                                 |

| PCB main link to AUX Spacing                    | 3x          | dielectric height | 3x of the thinner of above and below                                                                 |

| Max stub length on the Vias Allowed             |             |                   | Rout below core to minimize stub length                                                              |

| Max Intra-pair (within pair) Skew               | 1           | ps                | See Note 1 & 2                                                                                       |

| Max Inter-pair (pair-pair) Skew                 | 150         | ps                | See Note 1 & 2                                                                                       |

| Max GND transition via distance                 | < 1x        | diff pair pitch   | For signals switching reference layers, add<br>symmetrical ground stitching via near signal<br>vias. |

| Parameter                                                                                                                                                          | Requirement | Units | Notes         |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|---------------|--|--|--|

| AC coupling cap                                                                                                                                                    | 100         | nF    | Discrete 0402 |  |  |  |

| If routing to eDP device includes a flex or 2 <sup>nd</sup> PCB, the max trace & skew calculations must include all the PCBs/flex routing                          |             |       |               |  |  |  |

| Keep critical eDP related traces including differential clock/data traces away from other signal traces or unrelated power traces/areas or power supply components |             |       |               |  |  |  |

- Note: 1. Max Trace Delay & Max Trace Delay Skew matching must include substrate pin delays unless otherwise specified

- 2. Recommend doing trace length matching to <1ps before vias or any discontinuity to minimize common mode conversion

- 3. Asymmetric Stripline used on main board. Same configuration is recommended for module routing.

#### Table 5. eDP Auxiliary Channel Signal Routing Requirements

| Parameter                                                                            | Requirement       | Units             | Notes |

|--------------------------------------------------------------------------------------|-------------------|-------------------|-------|

| Termination, Reference plane, Max breakout,<br>Impedance, Max trace length, Max Vias | Same as Main Link |                   |       |

| PCB pair-to-pair spacing                                                             | 2x                | dielectric height |       |

| Max Intra-pair (within pair) Skew                                                    | Same as Main Link |                   |       |

| Max Inter-pair (pair-pair) Skew                                                      | No requirement    |                   |       |

Note: Asymmetric Stripline used on main board. Same configuration is recommended for module routing.

#### Table 6. eDP Interface Package & Jetson TK1 PCB Trace Delays

| Signal       | Package Delay<br>(ps) | Jetson PCB Delay<br>(ps) | Pkg + PCB Delay<br>(ps) | Max Trace Delay Allowed<br>(ps) | Available Max Trace Delay<br>for Module (ps) |

|--------------|-----------------------|--------------------------|-------------------------|---------------------------------|----------------------------------------------|

| LVDS0_TXD0_N | 50                    | 460                      | 510                     | 1480                            | 970                                          |

| LVDS0_TXD0_P | 51                    | 459                      | 510                     | 1480                            | 970                                          |

| LVDS0_TXD1_N | 44                    | 453                      | 497                     | 1480                            | 983                                          |

| LVDS0_TXD1_P | 45                    | 452                      | 497                     | 1480                            | 983                                          |

| LVDS0_TXD2_N | 30                    | 438                      | 468                     | 1480                            | 1012                                         |

| LVDS0_TXD2_P | 30                    | 437                      | 467                     | 1480                            | 1013                                         |

| LVDS0_TXD3_N | 46                    | 467                      | 513                     | 1480                            | 967                                          |

| LVDS0_TXD3_P | 47                    | 467                      | 514                     | 1480                            | 966                                          |

| LVDS0_TXD4_N | 38                    | 457                      | 495                     | 1480                            | 985                                          |

| LVDS0_TXD4_P | 38                    | 456                      | 494                     | 1480                            | 986                                          |

| DP_AUX_P     | 75                    | 379                      | 454                     | 1480                            | 1026                                         |

| DP_AUX_P     | 76                    | 379                      | 455                     | 1480                            | 1025                                         |

#### LVDS Design Guidelines

| Table 7. | LVDS Signal Routing Requirements |

|----------|----------------------------------|

|----------|----------------------------------|

| Parameter                                                                                                                                                           | Requirement | Units                | Notes                                                      |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------|------------------------------------------------------------|--|--|

| Max Frequency / Bit Rate                                                                                                                                            | 135 / 945   | MHz / Mbps           |                                                            |  |  |

| Number of Loads                                                                                                                                                     | 1           | load                 |                                                            |  |  |

| Topology                                                                                                                                                            |             |                      | Point-Point or Multi-drop, Differential,<br>Unidirectional |  |  |

| Termination                                                                                                                                                         | 100         | Ω                    | At the receiver (on die or on board)                       |  |  |

| Reference Plane                                                                                                                                                     | GND         |                      |                                                            |  |  |

| Trace Impedance Diff pair / Single Ended                                                                                                                            | 90 / 45-55  | Ω                    | +15%                                                       |  |  |

| Max Trace Length                                                                                                                                                    | 10 (1700)   | In (ps)              | See Note 1                                                 |  |  |

| PCB pair-to-pair spacing                                                                                                                                            | 3х          | dielectric<br>height | 3x of the thinner of above and below                       |  |  |

| Max Intra-pair (within pair) Skew                                                                                                                                   | 5           | ps                   | See Note 1                                                 |  |  |

| Max Inter-pair (pair-pair) Skew                                                                                                                                     | 100         | ps                   | See Note 1                                                 |  |  |

| If routing to LVDS device includes a flex or 2 <sup>nd</sup> PCB, the max trace & skew calculations must include all the PCBs/flex routing                          |             |                      |                                                            |  |  |

| Keep critical LVDS related traces including differential clock/data traces away from other signal traces or unrelated power traces/areas or power supply components |             |                      |                                                            |  |  |

Note: 1. Include Package & PCB routing delays for Max trace delays and max trace delay skew parameters.

2. Asymmetric Stripline used on main board. Same configuration is recommended for module routing.

| Signal       | Package Delay<br>(ps) | Jetson PCB Delay<br>(ps) | Pkg + PCB Delay<br>(ps) | Max Trace Delay Allowed<br>(ps) | Available Max Trace Delay<br>for Module (ps) |

|--------------|-----------------------|--------------------------|-------------------------|---------------------------------|----------------------------------------------|

| LVDS0_TXD0_N | 50                    | 460                      | 510                     | 1700                            | 1190                                         |

| LVDS0_TXD0_P | 51                    | 459                      | 510                     | 1700                            | 1190                                         |

| LVDS0_TXD1_N | 44                    | 453                      | 497                     | 1700                            | 1203                                         |

| LVDS0_TXD1_P | 45                    | 452                      | 497                     | 1700                            | 1203                                         |

| LVDS0_TXD2_N | 30                    | 438                      | 468                     | 1700                            | 1232                                         |

| LVDS0_TXD2_P | 30                    | 437                      | 467                     | 1700                            | 1233                                         |

| LVDS0_TXD3_N | 46                    | 467                      | 513                     | 1700                            | 1187                                         |

| LVDS0_TXD3_P | 47                    | 467                      | 514                     | 1700                            | 1186                                         |

| LVDS0_TXD4_N | 38                    | 457                      | 495                     | 1700                            | 1205                                         |

| LVDS0_TXD4_P | 38                    | 456                      | 494                     | 1700                            | 1206                                         |

Table 8. LVDS Interface Package & Jetson TK1 PCB Trace Delays

#### 2.1.2 Touch Guidelines

| Parameter                                                        | Requirement             | Units      | Notes      |

|------------------------------------------------------------------|-------------------------|------------|------------|

| Max Frequency                                                    | 50                      | MHz        |            |

| Configuration / Device Organization                              | 4                       | load       |            |

| Max Loading (total of all loads)                                 | 15                      | pF         |            |

| Reference plane                                                  | GND                     |            |            |

| Breakout Region Impedance                                        | Minimum width & spacing |            |            |

| Max PCB breakout delay                                           | 75                      | ps         |            |

| Trace Impedance                                                  | 50 - 60                 | Ω          | +15%       |

| Via proximity (Signal to reference)                              | < 3.8 (24)              | mm (ps)    | See Note 1 |

| Trace spacing Microstrip / Stripline                             | 4x / 3x                 | dielectric |            |

| Max Trace Delay                                                  | 890 (~5)                | ps (in)    | See Note 2 |

| Max Trace Delay Skew between MOSI (DOUT), MISO (DIN) & CS to SCK | 50                      | ps         |            |

Note: 1. Up to 4 signal vias can share a single GND return via

2. Include Package & PCB routing delays for Max trace delays and max trace delay skew parameters.

| Signal      | Package Delay<br>(ps) | Jetson PCB Delay<br>(ps) | Pkg + PCB Delay<br>(ps) | Max Trace Delay Allowed<br>(ps) | Available Max Trace Delay<br>for Module (ps) |

|-------------|-----------------------|--------------------------|-------------------------|---------------------------------|----------------------------------------------|

| TS_SPI_SCK  | 71                    | 521                      | 591                     | 890                             | 299                                          |

| TS_SPI_MOSI | 80                    | 490                      | 570                     | 890                             | 320                                          |

| TS_SPI_MISO | 56                    | 519                      | 575                     | 890                             | 315                                          |

| TS_SPI_CS_L | 76                    | 475                      | 550                     | 890                             | 340                                          |

Table 10. Touch SPI Interface Package & Jetson TK1 PCB Trace Delays

#### 2.1.3 I2C Design Guidelines

| Parameter       |                                            | Requirement              | Units      | Notes                                |

|-----------------|--------------------------------------------|--------------------------|------------|--------------------------------------|

| Max Frequency   | Standard / Fast Mode                       | 100 / 400                | kHz        | See Note 1                           |

| Max Loading     | Standard / Fast Mode                       | 400                      | pF         | Total of all loads                   |

| Reference plane |                                            | GND or PWR               |            |                                      |

| Trace Impedance |                                            | 50 - 60                  | Ω          | +15%                                 |

| Trace Spacing   |                                            | 1x                       | dielectric |                                      |

| Max Trace Delay | Standard Mode<br>Fast Mode, Fast Mode Plus | 3400 (~20)<br>1700 (~10) | ps (in)    | Include Package & PCB routing delays |

#### Table 11. I2C Interface Signal Routing Requirements for Standard & Fast Modes

Note: 1. For I2C interfaces that are pulled up to 1.8V, disable the OD (Open Drain) option for these pads. For I2C interfaces that are pulled up to 2.8V or higher, enable the OD (Open Drain) option.

- 2. Max Trace Delay must include Tegra K1 package pin delays, Jetson TK1 PCB trace delays & Module trace delays.

- 3. Due to the Jetson TK1 trace routing on GEN1\_I2C, the interface is limited to Standard Mode if used on a module.

#### Table 12. GEN2 I2C Interface Package & Jetson TK1 PCB Trace Delays

| Signal            | Package Delay<br>(ps) |     |     | -                |              | Available<br>Delay for<br>(p | Module       |

|-------------------|-----------------------|-----|-----|------------------|--------------|------------------------------|--------------|

|                   |                       |     |     | Standard<br>Mode | Fast<br>Mode | Standard<br>Mode             | Fast<br>Mode |

| GEN2_I2C_SCL_3.3V | 74                    | 354 | 428 | 3400             | 1700         | 2972                         | 1272         |

| GEN2_I2C_SDA_3.3V | 87                    | 337 | 424 | 3400             | 1700         | 2976                         | 1276         |

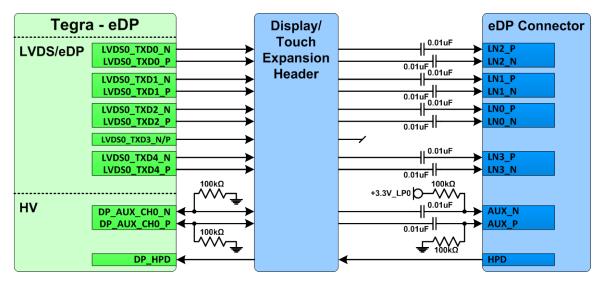

### 2.2 General Expansion Header

Jetson includes a 3x25, 2mm pitch female expansion header (reference designator J3A2), providing a number of interfaces to connect to Cameras and other peripherals including:

- CSI x4 lane IF for Camera 1 & x1 lane IF for Camera 2

- CAM\_I2C, Clock & Control GPIOs for both Cameras

- HSIC

- GEN1\_I2C

- UART2

- GPIO\_PU[6:0]

- Power-on, Reset & Force Recovery signals: Used for flashing initial SW image (or reflashing if corrupt)

- UART1 & PWR\_I2C: Used for Nvidia debug. Should not be used on module designs

#### Figure 6: General Expansion Header Connections

| Те     | gra                                 |                                                                     | General                    | Expansion Header                                  |                                                  |

|--------|-------------------------------------|---------------------------------------------------------------------|----------------------------|---------------------------------------------------|--------------------------------------------------|

| CSI    | CSI                                 | ── CSI x4 (Camera 1)→<br>── CSI x1 (Camera 2)→                      |                            | Camera 1 CSI<br>Camera 2 CSI<br>2.8V Cam          | +2.8V_RUN_CAM                                    |

| CAM    | CAM_I2C<br>GPIO PBB3                |                                                                     | I2C<br>Reset               | Common<br>Camera 1.8V Cam                         | +1.8V_RUN_CAM                                    |

|        | GPIO_PBB4                           |                                                                     | Flash                      | Control                                           | +2.8V_RUN_CAM_AF<br>$\overline{\mathbf{\nabla}}$ |

|        | GPIO_PBB5<br>GPIO_PBB7<br>GPIO_PCC1 | CAM1_MCLK<br>CAM1_PWDN<br>CAM1_AF_PWDN<br>CAM1_AF_PWDN<br>CAM1_GPIO | AF Powerdown<br>GPIO       | Camera 2.8V Cam<br>1 Clock &<br>Control 1.05V Cam | +1.05V_RUN_CAM_REAR                              |

|        | GPIO_PBB0<br>GPIO_PBB6<br>GPIO_PCC2 | CAM2_MCLK<br>CAM2_PWDN<br>CAM2_GPIO                                 | MCLK<br>Powerdown<br>GPIO  | Camera<br>2 Clock &<br>Control                    | +1.2V_RUN_CAM_FRONT                              |

| HSIC   | HSIC1                               | <−STROBE/DATA→                                                      | HSIC                       | General Use                                       | +1.2V GEN AVDD                                   |

| UART   | GEN1_I2C                            |                                                                     | 12C                        | General Use                                       |                                                  |

|        | GPIO_PU[6:0]<br>UART2               | · · · · · · · · · · · · · · · · · · ·                               | GPIOs<br>UART              | General Use<br>General Use<br>5.0V                | +5V_SYS                                          |

| SDMMC1 | CLK3_OUT                            | ← →                                                                 | Clock                      | General Use                                       |                                                  |

| SYS    | PWR_I2C                             | ← →                                                                 | 12C                        | Nvidia Use only                                   | +1.8V_VDDIO<br>Q                                 |

|        | KB_ROW9<br>KB_ROW10                 | ← 2-wire →                                                          | UART                       | Nvidia Use only                                   |                                                  |

|        | KB_COL0<br>GPIO_PI1                 | Gate ONKEY                                                          | Power-on<br>Force Recovery | For FLASHing Image                                |                                                  |

|        |                                     |                                                                     | System Reset               | ]                                                 |                                                  |

|        | To Power, For<br>& R                | eset Buttons                                                        |                            |                                                   |                                                  |

Figure 7. General Expansion Header Location on Jetson TK1 (J3A2)

#### Table 13. General Expansion Header Pin Descriptions

| Pin # | Signal Name         | Tegra K1 Ball | Usage/Description                   | Type/Dir<br>Default | Associated<br>Voltage Rail | Tegra<br>Pad<br>Type |

|-------|---------------------|---------------|-------------------------------------|---------------------|----------------------------|----------------------|

| 1     | +5V_SYS             | N/A           | Main 5V from system                 | Power               |                            |                      |

| 2     | CAM2_PWDN           | GPIO_PBB6     | Power Down for Camera 2             | Input               | +1.8V_RUN_CAM              | ST                   |

| 3     | +1.05V_RUN_CAM_REAR | N/A           | AMS PMIC LDO7 for Camera 1          | Power               |                            |                      |

| 4     | CAM2_MCLK           | GPIO_PBB0     | Master Reference Clock for Camera 2 | Input               | +1.8V_RUN_CAM              | ST                   |

| 5     | CAM_RST_L           | GPIO_PBB3     | Reset for Camera(s)                 | Input               | +1.8V_RUN_CAM              | ST                   |

| 6     | +2.8V_RUN_CAM       | N/A           | AMS PMIC LDO4 for Camera(s)         | Power               |                            |                      |

| 7     | CAM2_GPIO           | GPIO_PCC2     | GPIO for Camera 2                   | Bidir               | +1.8V_RUN_CAM              | ST                   |

| Pin # | Signal Name             | Tegra K1 Ball | Usage/Description                      | Type/Dir<br>Default | Associated<br>Voltage Rail | Tegra<br>Pad<br>Type |

|-------|-------------------------|---------------|----------------------------------------|---------------------|----------------------------|----------------------|

| 8     | CAM_I2C_SDA             | CAM_I2C_SDA   | I2C Data for Camera(s)                 | Bidir, Open Drain   | +1.8V_RUN_CAM              | DD                   |

| 9     | GND                     | N/A           | Tied to common GND                     | Ground              |                            |                      |

| 10    | GND                     | N/A           | Tied to common GND                     | Ground              |                            |                      |

| 11    | CAM_I2C_SCL             | CAM_I2C_SCL   | I2C Clock for Camera(s)                | Input, Open Drain   | +1.8V_RUN_CAM              | DD                   |

| 12    | CSI_A_CLK_P             | CSI_A_CLK_P   | CSI Clock (+) for Camera 1             | Output              | +1.2V_GEN_AVDD             | CSI                  |

| 13    | CSI_E_CLK_N             | CSI_E_CLK_N   | CSI Clock (-) for Camera 2             | Output              | +1.2V_GEN_AVDD             | CSI                  |

| 14    | GND                     | N/A           | Tied to common GND                     | Ground              |                            |                      |

| 15    | CSI_A_CLK_N             | CSI_A_CLK_N   | CSI Clock (-) for Camera 1             | Output              | +1.2V_GEN_AVDD             | CSI                  |

| 16    | CSI_E_CLK_P             | CSI_E_CLK_P   | CSI Clock (+) for Camera 2             | Output              | +1.2V_GEN_AVDD             | CSI                  |

| 17    | CSI_E_DO_N              | CSI_E_DO_N    | CSI Data Lane 0 (-) for Camera 2       | Output              | +1.2V_GEN_AVDD             | CSI                  |

| 18    | GND                     | N/A           | Tied to common GND                     | Ground              |                            |                      |

| 19    | GND                     | N/A           | Tied to common GND                     | Ground              |                            |                      |

| 20    | CSI_E_D0_P              | CSI_E_D0_P    | CSI Data Lane 0 (+) for Camera 2       | Output              | +1.2V_GEN_AVDD             | CSI                  |

| 21    | CSI_A_D1_N              | CSI_A_D1_N    | CSI Data Lane 1 (-) for Camera 1       | Output              | +1.2V_GEN_AVDD             | CSI                  |

| 22    | +1.2V_RUN_CAM_FRON<br>T | N/A           | AMS PMIC LDO5 for Camera 2             | Power               |                            |                      |

| 23    | GND                     | N/A           | Tied to common GND                     | Ground              |                            |                      |

| 24    | CSI_A_D1_P              | CSI_A_D1_P    | CSI Data Lane 1 (+) for Camera 1       | Output              | +1.2V_GEN_AVDD             | CSI                  |

| 25    | +2.8V_RUN_CAM_AF        | N/A           | AMS PMIC LDO10 for Camera 1            | Power               |                            |                      |

| 26    | +1.8V_VDDIO             | N/A           | AMS Switcher 5                         | Power               |                            |                      |

| 27    | GND                     | N/A           | Tied to common GND                     | Ground              |                            |                      |

| 28    | +1.2V_GEN_AVDD          | N/A           | AMS PMIC LDO2, used to sync HSIC rails | Power               |                            |                      |

| 29    | +1.8V_RUN_CAM           | N/A           | AMS PMIC LDO1                          | Power               |                            |                      |

| 30    | CSI_A_DO_N              | CSI_A_DO_N    | CSI Data Lane 0 (-) for Camera 1       | Output              | +1.2V_GEN_AVDD             | CSI                  |

| 31    | HSIC1_STROBE            | HSIC1_STROBE  | HSIC Strobe                            | Bidir               | +1.2V_GEN_AVDD             | HSIC                 |

| 32    | GND                     | N/A           | Tied to common GND                     | Ground              |                            |                      |

| 33    | CSI_A_DO_P              | CSI_A_DO_P    | CSI Data Lane 0 (+) for Camera 1       | Output              | +1.2V_GEN_AVDD             | CSI                  |

| 34    | GND                     | N/A           | Tied to common GND                     | Ground              |                            |                      |

| 35    | HSIC1_DATA              | HSIC1_DATA    | HSIC Data                              | Bidir               | +1.2V_GEN_AVDD             | HSIC                 |

| 36    | GND                     | N/A           | Tied to common GND                     | Ground              |                            |                      |

| 37    | +1.8V_VDDIO             | N/A           | AMS Switcher 5                         | Power               |                            |                      |

| 38    | GND                     | N/A           | Tied to common GND                     | Ground              |                            |                      |

| 39    | CSI_B_D1_N              | CSI_B_D1_N    | CSI Data Lane 3 (-) for Camera 1       | Output              | +1.2V_GEN_AVDD             | CSI                  |

| 40    | GPIO_PU0                | GPIO_PU0      | GPIO PUO: Available for general use    | Bidir               | +1.8V_VDDIO                | ST                   |

| Pin # | Signal Name      | Tegra K1 Ball          | Usage/Description                                       | Type/Dir<br>Default | Associated<br>Voltage Rail | Tegra<br>Pad<br>Type |

|-------|------------------|------------------------|---------------------------------------------------------|---------------------|----------------------------|----------------------|

| 41    | BR_UART1_TXD     | KB_ROW9                | For PM342 style Laguna FFD header                       | Input               | +1.8V_VDDIO                |                      |

| 42    | CSI_B_D1_P       | CSI_B_D1_P             | CSI Data Lane 3 (+) for Camera 1                        | Output              | +1.2V_GEN_AVDD             |                      |

| 43    | GPIO_PU1         | GPIO_PU1               | GPIO PU1: Available for general use                     | Bidir               | +1.8V_VDDIO                | ST                   |

| 44    | BR_UART1_RXD     | KB_ROW10               | For PM342 style Laguna FFD header                       | Output              | +1.8V_VDDIO                |                      |

| 45    | GND              | N/A                    | Tied to common GND                                      | Ground              |                            |                      |

| 46    | GPIO_PU2         | GPIO_PU2               | GPIO PU2: Available for general use                     | Bidir               | +1.8V_VDDIO                | ST                   |

| 47    | GND              | N/A                    | Tied to common GND                                      | Ground              |                            |                      |

| 48    | CSI_B_D0_P       | CSI_B_D0_P             | CSI Data Lane 2 (+) for Camera 1                        | Output              | +1.2V_GEN_AVDD             | CSI                  |

| 49    | GPIO_PU3         | GPIO_PU3               | GPIO PU3: Available for general use                     | Bidir               | +1.8V_VDDIO                | ST                   |

| 50    | PWR_I2C_SCL      | PWR_I2C_SCL            | Power I2C Clock: For Nvidia use only                    | Input, Open Drain   | +1.8V_VDDIO                | DD                   |

| 51    | CSI_B_DO_N       | CSI_B_DO_N             | CSI Data Lane 2 (-) for Camera 1                        | Output              | +1.2V_GEN_AVDD             | CSI                  |

| 52    | GPIO_PU4         | GPIO_PU4               | GPIO PU4: Available for general use                     | Bidir               | +1.8V_VDDIO                | ST                   |

| 53    | PWR_I2C_SDA      | PWR_I2C_SDA            | Power I2C Data: For Nvidia use only                     | Bidir, Open Drain   | +1.8V_VDDIO                | DD                   |

| 54    | GND              | N/A                    | Tied to common GND                                      | Ground              |                            |                      |

| 55    | GPIO_PU5         | GPIO_PU5               | GPIO PU5: Available for general use                     | Bidir               | +1.8V_VDDIO                | ST                   |

| 56    | GEN1_I2C_SCL     | GEN1_I2C_SCL           | GEN1 I2C Clock: 1.8V I2C IF available for general use   | Input, Open Drain   | +1.8V_VDDIO                | DD                   |

| 57    | CAM1_GPIO        | GPIO_PCC1              | GPIO for Camera 1                                       | Bidir               | +1.8V_RUN_CAM              | ST                   |

| 58    | GPIO_PU6         | GPIO_PU6               | GPIO PU6: Available for general use                     | Bidir               | +1.8V_VDDIO                | ST                   |

| 59    | GEN1_I2C_SDA     | GEN1_I2C_SDA           | GEN1 I2C Data: 1.8V I2C IF available for general use    | Bidir, Open Drain   | +1.8V_VDDIO                | DD                   |

| 60    | CAM1_AF_PWDN     | GPIO_PBB7              | Autofocus Powerdown for Camera 1                        | Input               | +1.8V_RUN_CAM              | ST                   |

| 61    | ONKEY_L          | KB_COL0<br>(indirect)  | Power On (to PMU ONKEY & gated version to Tegra)        | Bidir               | +2.5V_AON_RTC              |                      |

| 62    | GND              | N/A                    | Tied to common GND                                      | Ground              |                            |                      |

| 63    | CAM_FLASH        | GPIO_PBB4              | Flash enable to control camera flash driver             | Input               | +1.8V_RUN_CAM              | ST                   |

| 64    | PMU_RESET_IN_L   | N/A                    | System Reset signal                                     | Bidir               | +2.5V_AON_RTC              |                      |

| 65    | UART2_RXD        | UART2_RXD              | UART 2 Receive                                          | Output              | +1.8V_VDDIO                | ST                   |

| 66    | CAM1_PWDN        | GPIO_PBB5              | Powerdown for Camera 1                                  | Input               | +1.8V_RUN_CAM              | ST                   |

| 67    | FORCE_RECOVERY_L | GPIO_PI1<br>(indirect) | Force Recovery: To enter Forced Recovery mode           | Bidir               | +2.5V_AON_RTC              |                      |

| 68    | UART2_TXD        | UART2_TXD              | UART 2 Transmit                                         | Input               | +1.8V_VDDIO                | ST                   |

| 69    | CAM1_MCLK        | CAM_MCLK               | Master Reference Clock for Camera 1                     | Input               | +1.8V_RUN_CAM              | ST                   |

| 70    | CLK3_OUT         | CLK3_OUT               | Clock 3 Output: Available clock source from<br>Tegra K1 | Input               | +1.8V_RUN_CAM              | ST                   |

| 71    | UART2_CTS_L      | UART2_CTS_L            | UART 2 Clear to Send                                    | Output              | +1.8V_VDDIO                | ST                   |

| Pin # | Signal Name | Tegra K1 Ball | Usage/Description      | Type/Dir<br>Default | Associated<br>Voltage Rail | Tegra<br>Pad<br>Type |

|-------|-------------|---------------|------------------------|---------------------|----------------------------|----------------------|

| 72    | NC          | N/A           | Not used               |                     |                            |                      |

| 73    | GND         | N/A           | Tied to common GND     | Ground              |                            |                      |

| 74    | UART2_RTS_L | UART2_RTS_L   | UART 2 Request to Send | Input               | +1.8V_VDDIO                | ST                   |

| 75    | NC          | N/A           | Not used               |                     |                            |                      |

Notes: - In the Type/Dir column, Output is from Module. Input is to Module. Bidir is for Bidirectional signals. - See Section 5.0 for details on the standard Tegra Pad Types (ST & DD)

#### 2.2.1 Camera/CSI Guidelines

Figure 8: Dual Camera Connection Example

| Table 14 | MIDI CCI Interfee | o Cianal Douting | Doquiromonto |

|----------|-------------------|------------------|--------------|

|          | MIPI CSI Interfac | e signal Routing | Requirements |

| Parameter                                          | Requirement | Units      | Notes      |

|----------------------------------------------------|-------------|------------|------------|

| Max Frequency/Data Rate (per data lane)            | 750 / 1500  | MHz/Mbps   |            |

| Number of Loads / loading per pin                  | 1 / 10      | Load / pf  |            |

| Reference plane                                    | GND or PWR  |            | See Note 1 |

| Breakout Region Impedance Diff pair / Single Ended | 90 / 45-55  | Ω          | +15%       |

| Max PCB breakout delay                             | 48          | ps         |            |

| Trace Impedance Diff pair / Single Ended           | 90 / 45-55  | Ω          |            |

| Via proximity (Signal to reference)                | < 3.8 (24)  | mm (ps)    | See Note 2 |

| Trace spacing Microstrip / Stripline               | 2x / 2x     | dielectric |            |

| Max Trace Delay                                    | 1620        | ps         | See Note 3 |

| Max Intra-pair Skew                                | 1           | ps         | See Note 3 |

| Max Trace Delay Skew between DQ & CLK              | 10          | ps         | See Note 3 |

Note: 1. If PWR, 0.01uF decoupling cap required for return current

- 2. Up to 4 signal vias can share a single GND return via

- 3. Include Package & PCB routing delays for Max trace delays and max trace delay skew parameters.

| Signal      | Package Delay<br>(ps) | Jetson PCB Delay<br>(ps) | Pkg + PCB Delay<br>(ps) | Max Trace Delay Allowed<br>(ps) | Available Max Trace Delay<br>for Module (ps) |

|-------------|-----------------------|--------------------------|-------------------------|---------------------------------|----------------------------------------------|

| CSI_A_CLK_N | 46                    | 567                      | 613                     | 1620                            | 1007                                         |

| CSI_A_CLK_P | 46                    | 567                      | 613                     | 1620                            | 1007                                         |

| CSI_A_DO_N  | 81                    | 531                      | 612                     | 1620                            | 1008                                         |

| CSI_A_D0_P  | 81                    | 530                      | 611                     | 1620                            | 1009                                         |

| CSI_A_D1_N  | 61                    | 560                      | 621                     | 1620                            | 999                                          |

| CSI_A_D1_P  | 62                    | 559                      | 621                     | 1620                            | 999                                          |

| CSI_B_DO_N  | 78                    | 558                      | 636                     | 1620                            | 984                                          |

| CSI_B_D0_P  | 79                    | 556                      | 635                     | 1620                            | 985                                          |

| CSI_B_D1_N  | 66                    | 572                      | 638                     | 1620                            | 982                                          |

| CSI_B_D1_P  | 67                    | 572                      | 639                     | 1620                            | 981                                          |

| CSI_E_CLK_N | 67                    | 391                      | 458                     | 1620                            | 1162                                         |

| CSI_E_CLK_P | 68                    | 390                      | 458                     | 1620                            | 1162                                         |

| CSI_E_D0_N  | 57                    | 398                      | 455                     | 1620                            | 1165                                         |

| CSI_E_D0_P  | 58                    | 397                      | 455                     | 1620                            | 1165                                         |

#### Table 15. CSI Interface Package & Jetson TK1 PCB Trace Delays

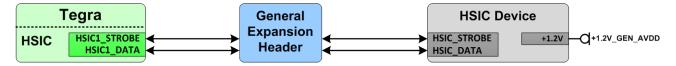

#### 2.2.2 HSIC Guidelines

#### Figure 9: HSIC Connection Example

#### Table 16. HSIC Interface Signal Routing Requirements

| Parameter                                               | Requirement       | Units           | Notes      |

|---------------------------------------------------------|-------------------|-----------------|------------|

| Max Frequency (High Speed) Bit Rate / UI period / Freq. | 480 / 2.083 / 240 | Mbps / ns / MHz |            |

| Input Buffer Loading                                    | 1 - 5             | pF              |            |

| Reference plane                                         | GND               |                 |            |

| Max PCB breakout delay                                  | 17                | ps              |            |

| Trace Impedance                                         | 50                | Ω               | +15%       |

| Via proximity (Signal to reference)                     | < 3.8 (24)        | mm (ps)         | See Note 1 |

| Trace spacing Microstrip / Stripline                    | 4x / 3x           | dielectric      |            |

| Trace Delay Min / Max                                   | 133 (667)         | Mm (ps)         | See Note 2 |

| Max Trace Delay Skew between HSIC[2:1]_STROBE & DATA    | 15                | ps              | See Note 2 |